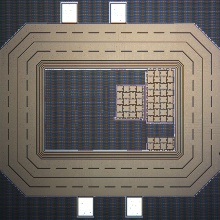

Circuit Design in Nanometer Scaled CMOS

Summary

The continuing strive for smaller CMOS technology nodes pushes the need for new and improved modeling of MOS transistors as well as the need for advanced circuit topologies. In modern integrated circuits, MOS transistors are operated in regions where the classical square-law model may be insufficient. Furthermore, the small structure sizes can have serious effects on the transistor’s behavior. It is therefore very important to understand such effects and to use new MOS transistor models for the design of integrated circuits in submicron CMOS technologies. The decrease in structure size leads also to an decrease of the supply voltages, which demands for new circuit topologies. In this module, the students will be introduced to these new challenges in advanced nanometer-scaled CMOS circuit design.

Contents

- Layout and matching of integrated circuit elements

- Modeling of MOS transistors operated in strong and weak inversion with respect to the problems originating from the small structure sizes in nanometer-scaled CMOS technologies

- Matching and matching-aware design of MOS transistors

- Advanced test benches for the design and simulation of operational amplifiers

- Advanced operational amplifier circuits in nanometer-scaled CMOS technologies

- Advanced fully differential operational amplifiers

Organization

- Lecture: Prof. Jens Anders

- Exercise: M. Sc. Mahmut Coban

- Module description, contents, and timetable in C@mpus

- Lecture notes in ILIAS

Contact

Jens Anders

Prof. Dr.Institute Director